Nomita Goswami

FirstEDA

Nomita Goswami

FirstEDA

Many of you may be familiar with, or indeed use, Aldec Riviera-PRO as a simulator. But did you know that you can also use Riviera-PRO to generate an error-free Universal Verification Methodology Register Abstraction Layer (UVM RAL) model? This feature enables you to automatically generate a UVM RAL model from your input specification, saving you the laborious task of handcrafting hundreds, or even thousands, of register models. For those of you who are not familiar with the UVM Register Model, in a nutshell it’s the testbench equivalent of design registers.

The idea behind creating the UVM RAL model revolves around the word ‘REUSE’. It links the register names to their addresses. The purpose of the UVM Register layer is to abstract the test from low-level details of the registers inside the device under test (DUT). This abstraction provides many benefits, including:

If you are wondering why UVM for Register Modelling is a good choice, consider these two reasons to justify its use:

Unfortunately, the benefits of using the register layer come at the cost of specifying the register models in the testbench to reflect the registers in the hardware. With thousands, or even tens of thousands of registers in a typical design, this can be a tedious and error-prone process when performed manually.

Using Riviera-PRO, the UVM RAL model can be automatically generated from the IP component specification, along with the test environment and packages. The process supports two input formats: CSV and IP-XACT.

Below is the command to generate all the models from IP-XACT description v.2009 using the command line utility ‘register_generator’ in Riviera-PRO:

register_generator ipx –v2009 reg_desc.xml –all

In addition to the UVM RAL model with coverage, generation of RTL Models in VHDL, Verilog/SystemVerilog, C-headers and HTML documentation is also possible.

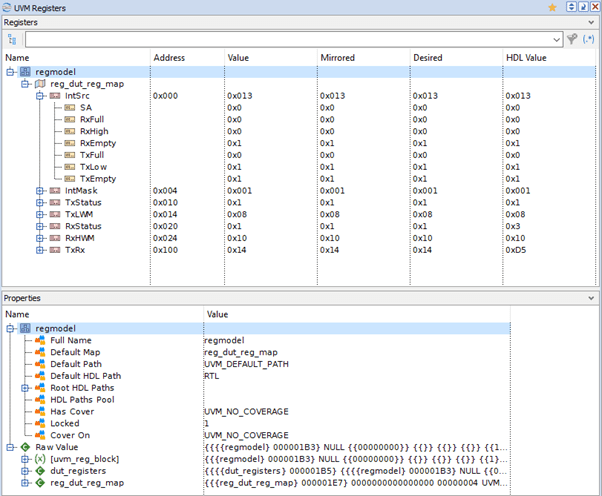

Riviera-PRO supports UVM Verification, making it easy to integrate the generated UVM RAL Model into the UVM testbench to verify. To aid its view Riviera-PRO now also has a UVM Register window, where the register model can be viewed as a hierarchy of register blocks, or as a memory map with their properties, as shown below:

I recommend looking into the register generator capabilities of Aldec’s Riviera-PRO, if you haven’t already done so. The entire flow has been presented recently in an Aldec webinar (Verifying Zynq MPSoC Designs? Learn how UVM Register Access Layer (RAL) can help) where you can also learn more abouts its role in highly configurable IP-based designs that have become the norm in this SoC era.

Interested in finding out more? Please contact us using the form here. We will be delighted to discuss your requirements and arrange a demonstration.