Wojtek Lewandowski

ALDEC Senior Hardware Systems Designer

Wojtek Lewandowski

ALDEC Senior Hardware Systems Designer

SOC Verification Never Been Easier

—

At the beginning of September, Aldec announced the new version of HES.Proto-AXI software, our host to FPGA bridge solution. This tool supports QEMU for Co-Verification purposes which is considered as one of the main features. QEMU is an open-source machine emulator and virtualiser that emulates a wide range of CPU architectures. This flexibility helps software and embedded engineers in the testing process significantly. Heterogeneous SoC architectures such as Zynq has become very popular recently due to the combination of programmable logic (FPGA) and processing system (ARM) integrated into a single chip. Developing a design using such hybrid systems causes complexity in design verification stages. Aldec provides the HW/SW co-simulation platform for hybrid systems using QEMU and HES.Proto-AXI tool. In this blog, you will learn more about how this solution works and how it simplifies the verification process for your challenging hybrid designs.

The question is how to comprehensively test such mixed technology devices? Aldec responses to this question, as a pioneer in mixed HDL language simulation and hardware-assisted verification is – hybrid devices require a hybrid verification environment. Aldec has been integrating QEMU and its tools for some time now and guess what? The recently announced QEMU and HES.Proto-AXI integration is not the only one!

QEMU with Aldec tools

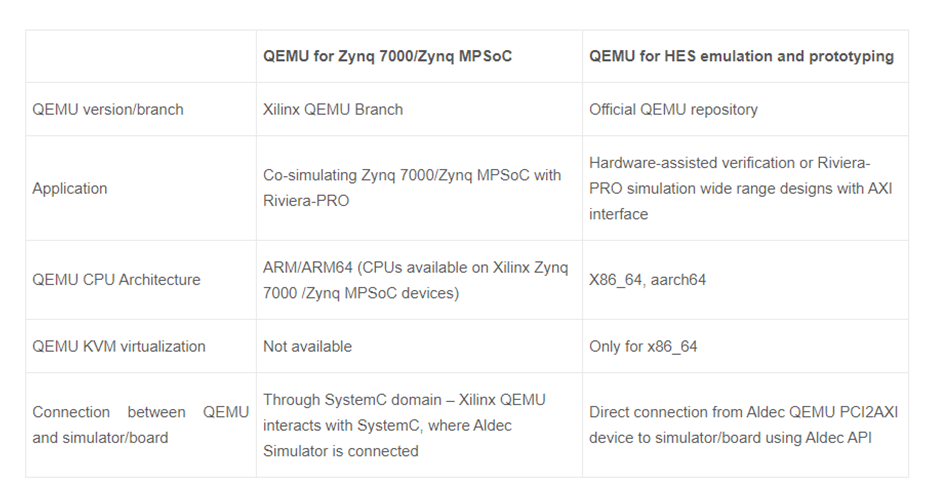

There are several places in the whole range of Aldec products and tools that QEMU fits perfectly. The most general breakdown can be made based on the project requirements:

Based on the above division, we offer two solutions: QEMU for Zynq/Zynq MPSoC and QEMU for HES emulation and prototyping.

Aldec QEMU co-simulation for Xilinx Zynq 7000/Zynq MPSoC devices

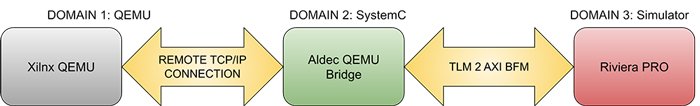

To Co-Simulate the designs that are based on Xilinx Zynq 7000 / MPSoC devices, Aldec has provided a HW/SW Co-Simulation solution using Riviera-Pro (Advance RTL simulator) and Xilinx QEMU. This solution is provided on TySOM EDK package which simplified the hybrid verification for Xilinx Zynq devices. This integration makes an environment for engineers to verify the entire SoC (Processing System and Programmable logic) simultaneously. Separate tests for CPU and FPGA are no longer the only testing method. This solution utilises Xilinx QEMU and connects it to Riviera-PRO giving a comprehensive environment for testing Linux, drivers, or standalone processor applications with FPGA design in the simulator.

Figure 1: Xilinx Zynq/Zynq MPSoC QEMU and Riviera-PRO co-simulation

Aldec QEMU co-verification environment for emulation and prototyping

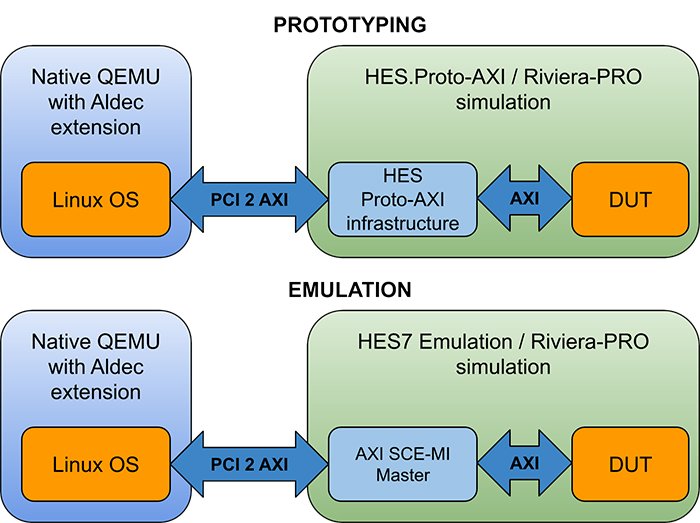

QEMU integration with Aldec emulation and prototyping products differs from the solution of Xilinx Zynq 7000/Zynq MPSoC. Years spent on the hardware-assisted verification market shown that one of the most important things is scalability to various verification modes. To achieve that we have adapted the official open-source QEMU to interact with:

The architecture of the co-verification environment is shown in Figure 2.

Figure 2: Aldec QEMU emulation and prototyping co-verification environment

The environment consists of:

Conclusion

The need for a comprehensive SoC verification is being noticed more and more due to the significant growth in demand for such devices. Having both HW/SW in an SoC design requires a hybrid environment to verify both and to make sure new changes don’t affect the entire design functionality. Aldec has paved this path by preparing a hybrid environment combining QEMU with Aldec verification, emulation and prototyping tools to solve the complexity of SoC verification process. This solution meets different verification requirements (Xilinx Zynq /Zynq MPSoC, ASIC emulation and prototyping) and offers various features. First of all, it corresponds to the architecture of SoC designs and gives an opportunity to test software and hardware live. It emulates different architecture CPUs, simplifies and accelerates cross-development between hardware and software/embedded engineering teams. Last but definitely not least – it’s integrated with Aldec SoC/ASIC/FPGA verification products such as HES high speed prototyping boards, HES-DVM, Riviera-PRO simulator and HES.Proto-AXI architecture.