Farhad Fallahlalehzari

ALDEC Applications Engineer

Farhad Fallahlalehzari

ALDEC Applications Engineer

Aldec’s Co-Simulation Solution using QEMU and Riviera-PRO

—

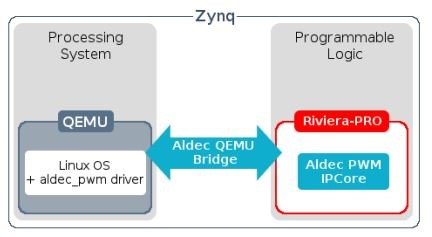

Heterogeneous System on Chip (SoC) devices like the Xilinx Zynq 7000 and Zynq UltraScale+ MPSoC combine a high-performance processing system (PS) with state-of-the-art programmable logic (PL). This combination allows a system to be architected to provide an optimally balanced single-chip software / hardware solution. However, all too often, the integration between the PS and PL takes place late in the design cycle, when the impact of addressing issues raised is larger in both time and cost. Verifying the interaction between the PS and PL presents a challenge to the design team. However, each aspect can be verified together, using QEMU (Quick Emulator) for the PS and Riviera-PRO for the PL.

Let’s consider a project using one of Aldec’s embedded development boards “TySOM-2-7Z100”, which contains the largest Xilinx Zynq-7000 SoC device. QEMU would emulate the PS architecture, which is ARM Cortex-A9 in this example. In parallel, the HW would be simulated and verified inside Riviera-PRO.

An example is shown in figure 1. In this example, TySOM boards are targeted as the main board. TySOM boards provide a wide variety of peripherals such as USB 3.0, HDMI 2.0 and 1.4, DisplayPort, QSFP+, mPCIe, FMC connectors and etc. Complete reference designs for applications such as ADAS, IoT and Networking are provided on the package.

This is a simple PWM example which is implemented into the FPGA. This module is controlled with the ARM processor inside Zynq device which is emulated by QEMU.

Figure 1: QEMU & Riviera-PRO HW/SW Co-Verification diagram

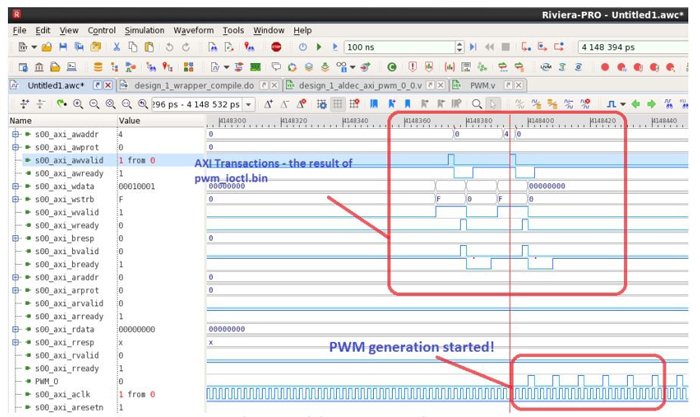

In this example, by running the SW application inside QEMU, the AXI transactions are trackable in Riviera-PRO Waveform Viewer during HW/SW co-simulation. These transactions are shown in figure 2.

Figure 2: AXI transactions shown inside Riviera-PRO

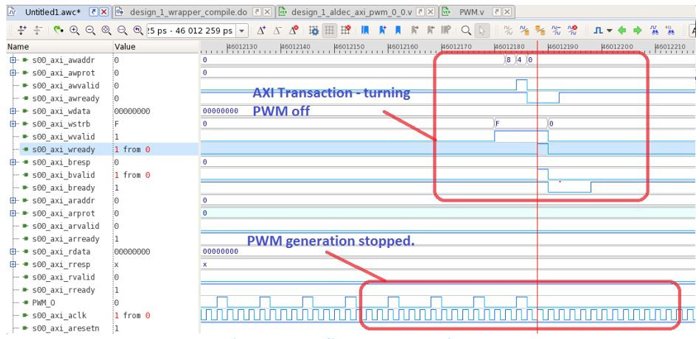

To stop the PWM generation, the stop signal should be sent by the SW executing in QEMU to the hardware IP in the PL. Figure 3, shows the results of finishing the PWM generation.

Figure 3: AXI transactions as the results of PWM stop signal

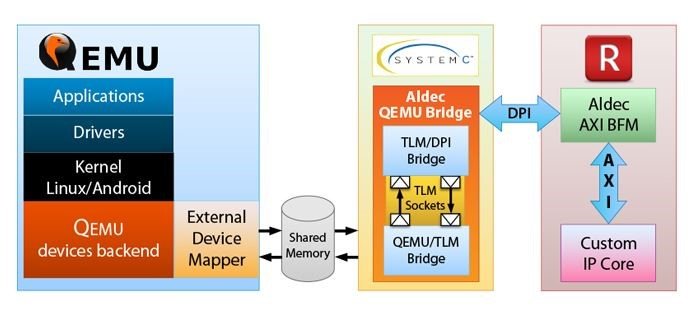

System integration and co-simulation of HDL code with software applications/drivers executing in QEMU is now simplified with the addition of the Aldec QEMU Bridge. It connects Riviera-PRO and QEMU, and converts SystemC TLM transactions to AXI and vice-versa providing a fast interface for co-simulation which can be seen in figure 4.

For the simulation of customer-designed IP cores with AXI3, AXI4 and AXI4lie, AXI Bus Functional Modules (BFM) are required. Attributes of these modules allow users to test IP cores functioning in conditions close to a real-life work environment. This, along with possible randomisation of input parameters, helps in detecting errors and protecting designed IP cores from undesired events. Aldec also provides the BFM supporting AXI3, AXI4 and AXI4lite protocols. For more detail about AXI interface, you can visit here.

Figure 4: Detail information of HW/SW co-simulation solution

This solution gives the full debug capabilities of RTL IP core in Riviera-PRO simulator. Kernel and driver debug could be done using GDB. One of the interesting features is the ability to add HW and SW breakpoints.

To sum up, the solution covered in this blog will enable us to identify and debug issues which reside in both the software and hardware design. Co-Simulation enables you to develop your application faster and reduce the bring-up time once the application hardware arrives for integration. Aldec offers TySOM EDK, a package including Riviera-PRO and a TySOM board, to fulfil SoC design engineers’ need.