RTAX/RTSX

PROTOTYPING MICROSEMI RAD TOLERANT DEVICES / FPGA / PROTO

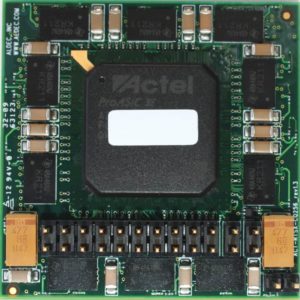

Aldec and Microsemi have joined forces to offer an innovative, reprogrammable prototyping solution for Microsemi RTAX-S/SL, RTAX-DSP and RTSX-SU space-fight system designs. Unlike the traditional One Time Programmable (OTP) anti-fuse space-qualified FPGAs, the Aldec prototype adaptor uses flash-based, Microsemi ProASIC 3E FPGA technology for design prototype re-programmability.

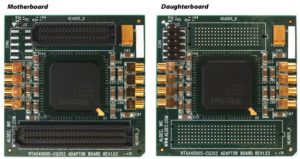

The RTAX-S/SL and RTSX-SU prototyping solution from Aldec allows designs that use these Microsemi devices to be prototyped with a reprogrammable FPGA device. This not only speeds up the development process but also mitigates risk by using a proven development methodology. Alternative methodologies that use reprogrammable devices during initial design development can be both costly and unreliable, due to the additional components required to support the development FPGA. The Aldec solution with its pin-for-pin compatible adaptor avoids such issues.

The software conversion tool automatically converts the RTAX-S/SL and RTSX-SU EDIF netlist into a ProASIC3E EDIF netlist, eliminating the requirement to perform manual mapping of RTAX and RTSX primitives and memory blocks to ProASIC3E devices. Aldec’s prototyping adaptor boards and netlist converter reduces overall project costs and shortens design validation time of the RTAX-S/SL and RTSX-SU project.

The pin remapping utility allows automatic Physical Design Constraint (PDC) file conversion, which eliminates the need for additional manual work.

The Aldec RTAX development solution has been successfully used in numerous flight proven designs.

The RTAX/RTSX prototyping adapter provides a fast, efficient and effective way of targeting a variety of Microsemi’s high reliability, radiation tolerant, antifuse FPGAs and flash-based ProASIC3 devices.

Features and Benefits

Supported Microsemi devices/capacities:

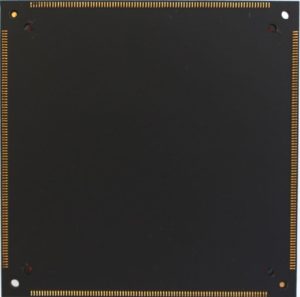

- RTAX-S/SL up to 4000S, RTAX-DSP and RTSX-SU device

Automated Device Netlist Converter:

- Memory conversion

- Physical Design Constraint (PDC) file conversion

FirstEDA has experience of working with Europe’s leading space industry experts. We provide leading-edge solutions to resolve the issues involved in developing and debugging designs targeted to Microsemi’s OTP anti-fuse space-qualified FPGAs. FirstEDA regularly presents to Europe’s leading satellite technologists at events such as the Microsemi Space Forum.

Adam Wilson, Sales, FirstEDA

Adam Wilson, Sales, FirstEDA

“Microsemi’s high performance, high density, radiation-tolerant FPGA’s are used widely in military and space applications. The nature of these anti-fuse devices means that unlike other FPGA’s, they are not re-programable. This could lead to very costly issues if a bug was to make it through to the final design.

Through an official partnership with Microsemi, Aldec offers an innovative, reprogrammable prototyping solution which uses flash-based FPGA technology for design prototype re-programmability.“