Aldec

DESIGN & VERIFICATION

FPGA / SAFETY / ASIC / FV / ReqM / HW-V / PROTO

DESIGN & VERIFICATION

FPGA / SAFETY / ASIC / FV / ReqM / HW-V / PROTO

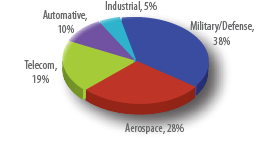

Aldec delivers high quality EDA solutions for government, military, aerospace, telecommunications, automotive and safety critical applications.

Large companies including IBM, Qualcomm, Rohde and Schwarz, Bosch, Texas Instruments, Applied Micro, Hewlett Packard, Toshiba, Intel, NEC, LG, Hitachi, NASA, Raytheon, Panasonic, Lockheed Martin, Samsung, as well as mid-size and small firms use Aldec EDA verification suites to boost product performance, cut design development cycles and reduce cost.

Why choose Aldec?

Today’s FPGA design teams require innovative solutions that foster team productivity and enable rapid deployment at every stage of design development – from Design Entry to Place and Route. Aldec offers the industry’s most comprehensive, all-in-one platform for FPGA design development to meet the increasing demands of the FPGA development process.

Active-HDL is a Windows-based, integrated design creation and simulation solution for engineers working on projects ranging from simple PLD ‘glue logic’ all the way up to several-million-gate system-on-chip FPGAs.

ALINT-PRO is a design rule checking (DRC) tool. It uses rule files (‘policies’) to check that a design’s RTL adheres to a defined RTL coding style. It decreases development time dramatically by identifying design issues early in the development schedule.

Riviera-PRO addresses the verification requirements of engineers targeting large gate-count FPGAs, ASICs and System-on-Chip devices. It gives engineers the ultimate testbench in terms of productivity, reusability and automation; all by combining a high-performance simulation engine with advanced debugging capabilities (at different levels of abstraction).

Aldec’s functional verification platform is an integrated portfolio of tools that drive productivity and innovation by enabling industry-leading technologies for design entry, mixed-language HDL simulation, mixed-signal simulation, DSP co-simulation, integrated and unified visual debugging, assertions, coverage, and static design analysis.

All components of the platform support the latest industry standards (VHDL, Verilog, Verilog-AMS, SystemVerilog, SystemC) and methodologies (OVM/UVM, OSVVM, UVVM, VMM), enabling you to address verification challenges of your today’s and tomorrow’s FPGA, SoC or ASIC designs.

Active-HDL is a Windows-based, integrated design creation and simulation solution for engineers working on projects ranging from simple PLD ‘glue logic’ all the way up to several-million-gate system-on-chip FPGAs.

ALINT-PRO is a design rule checking (DRC) tool. It uses rule files (‘policies’) to check that a design’s RTL adheres to a defined RTL coding style. It decreases development time dramatically by identifying design issues early in the development schedule.

Riviera-PRO addresses the verification requirements of engineers targeting large gate-count FPGAs, ASICs and System-on-Chip devices. It gives engineers the ultimate testbench in terms of productivity, reusability and automation; all by combining a high-performance simulation engine with advanced debugging capabilities (at different levels of abstraction).

With the growing complexity and size of today’s FPGA and ASIC designs, requirements have also grown exponentially, and methodologies to effectively manage and track requirements have never been more crucial to produce high-quality, reliable and safe products on time and within budget. Aldec’s requirements lifecycle management tool suite streamlines the requirements engineering process from capture to traceability, analysis to reporting and design to test results management.

Spec-TRACER is a unified requirements lifecycle management solution designed specifically for FPGA and ASIC designs. It facilitates requirements capture, management, impact analysis, traceability and reporting. Spec-TRACER seamlessly integrates with your Windows-based HDL design and simulation tools and also integrates directly with IBM Rational DOORS.

DO-254 is a means of compliance for the development of airborne electronic hardware containing FPGAs, PLDs and ASICs. FPGA design and verification under DO-254 guidelines is a rigorous undertaking, and requires special features and capabilities from design, simulation and hardware verification tools. The Federal Aviation Administration (FAA) and other international certification authorities recognise the use of commonly used tools for FPGA design and verification such as RTL Simulators, Synthesis, Place & Route and Static Timing Analysis.

ALINT-PRO is a design rule checking (DRC) tool. It uses rule files (‘policies’) to check that a design’s RTL adheres to a defined RTL coding style. It decreases development time dramatically by identifying design issues early in the development schedule.

Spec-TRACER is a unified requirements lifecycle management solution designed specifically for FPGA and ASIC designs. It facilitates requirements capture, management, impact analysis, traceability and reporting. Spec-TRACER seamlessly integrates with your Windows-based HDL design and simulation tools and also integrates directly with IBM Rational DOORS.

DO-254/CTS is a fully customised hardware and software platform that augments target board testing to increase verification coverage by test and to satisfy the verification objectives of DO-254/ED-80.

The complexity and size of modern ASICs has surpassed what can be simulated with conventional RTL simulators. This has resulted in a renaissance for hardware assisted verification, also referred to as emulation. As well as significant hardware verification problems, the amount of software, specifically hardware dependent software, has also increased in today’s SoC. For some time now FPGA prototypes have been used as the pre-silicon software development platform. Such systems are now being used earlier in the design process, resulting in greater use of FPGA based systems for hardware verification.

HES-DVM is a fully automated verification and validation system for SoC ASIC designs of 200M+ ASIC gates. Aldec’s FPGA Hardware Emulation Solution is based on the latest Xilinx Virtex-7 devices and is capable of simulation acceleration, and SCE-MI transaction co-emulation.

HES-7 provides SoC and ASIC verification and validation teams with a scalable and high-quality FPGA-based ASIC prototyping solution. Each HES-7 board with dual Xilinx Virtex-7 2000T has 4million FPGA logic cells (or up to 24million ASIC gates of capacity) not including the DSP and memory resources.

Whether the design targets an ASIC, ASSP or FPGA, design prototyping is an essential verification methodology in every IC project. Prototyping can be implemented in various hardware configurations and technology depending on the design complexity, but in all cases the use of FPGA-based platforms have become the de-facto due to the versatility and maturity of FPGAs.

HES-DVM is a fully automated verification and validation system for SoC ASIC designs of 200M+ ASIC gates. Aldec’s FPGA Hardware Emulation Solution is based on the latest Xilinx Virtex-7 devices and is capable of simulation acceleration, and SCE-MI transaction co-emulation.

HES-7 provides SoC and ASIC verification and validation teams with a scalable and high-quality FPGA-based ASIC prototyping solution. Each HES-7 board with dual Xilinx Virtex-7 2000T has 4million FPGA logic cells (or up to 24million ASIC gates of capacity) not including the DSP and memory resources.

Aldec and Microsemi have joined forces to offer an innovative, reprogrammable prototyping solution for Microsemi RTAX-S/SL, RTAX-DSP and RTSX-SU space-fight system designs. Unlike the traditional One Time Programmable (OTP) anti-fuse space-qualified FPGAs, the Aldec prototype adaptor uses flash-based, Microsemi ProASIC 3E FPGA technology for design prototype re-programmability.

TySOM is a family of development boards for embedded applications that features Xilinx Zynq all programmable module combining FPGA with ARM Cortex processor. Plethora of included peripherals makes these boards useful in various embedded applications like Automotive, IoT, Industrial automation or embedded HPC.

Driven by the large NRE and TTM pressures of consumer electronics, it’s vital that an ASIC is right first time. This has resulted in the task of verification closure becoming critical for success of the project and in many cases the company. For this reason new methods to improve overall coverage and efficiency are being adopted by leading ASIC project teams.

ALINT-PRO is a design rule checking (DRC) tool. It uses rule files (‘policies’) to check that a design’s RTL adheres to a defined RTL coding style. It decreases development time dramatically by identifying design issues early in the development schedule.

Riviera-PRO addresses the verification requirements of engineers targeting large gate-count FPGAs, ASICs and System-on-Chip devices. It gives engineers the ultimate testbench in terms of productivity, reusability and automation; all by combining a high-performance simulation engine with advanced debugging capabilities (at different levels of abstraction).

HES-DVM is a fully automated verification and validation system for SoC ASIC designs of 200M+ ASIC gates. Aldec’s FPGA Hardware Emulation Solution is based on the latest Xilinx Virtex-7 devices and is capable of simulation acceleration, and SCE-MI transaction co-emulation.

HES-7 provides SoC and ASIC verification and validation teams with a scalable and high-quality FPGA-based ASIC prototyping solution. Each HES-7 board with dual Xilinx Virtex-7 2000T has 4million FPGA logic cells (or up to 24million ASIC gates of capacity) not including the DSP and memory resources.

BLOG: 35-years-old, and still on point

BLOG: Problems Accessing Registers? – See how UVM RAL can help

BLOG: FPGA vs GPU for Machine Learning Applications: Which one is better?

VIDEO: Aldec Overview

VIDEO: Introduction to FPGA Simulation

VIDEO: Writing a Verilog Testbench

VIDEO: Writing a SystemC Testbench

VIDEO: ALINT-PRO 1.1 Basics: Running Design Entry and Linting

RELEASE: Hardware Lifecycle Data Management for Teams

ARTICLE: View from Above

ARTICLE: Visible Benefits