Register Design Entry

Equipped with user-friendly templates, you can specify your registers using any of the add-ins to Word, Excel, OpenOffice Calc or FrameMaker. Built with high-performance IP-XACT compiler and SystemRDL compiler, simple and complex registers can be created hierarchically such that large SoC designs are divided into manageable sub-blocks that are represented symbolically, designed and connected together. This methodology enables you to work on different parts of the design in parallel with a large team. Users are able to convert register spec from IP-XACT to UVM or from SystemRDL to IP-XACT.

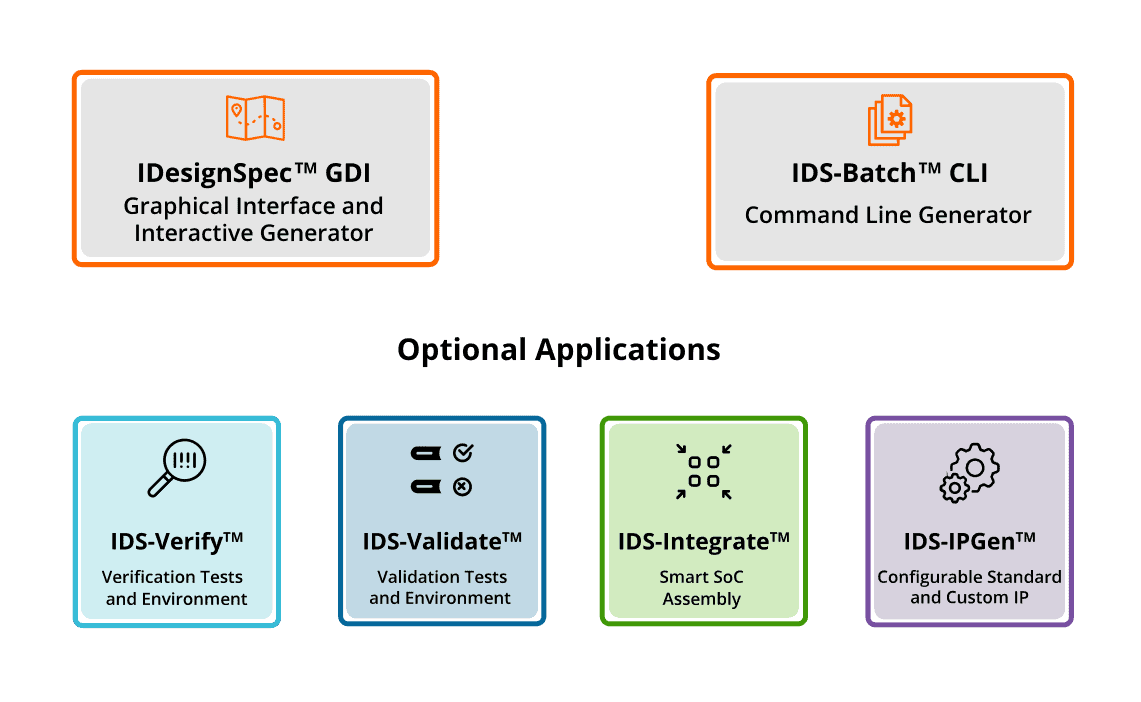

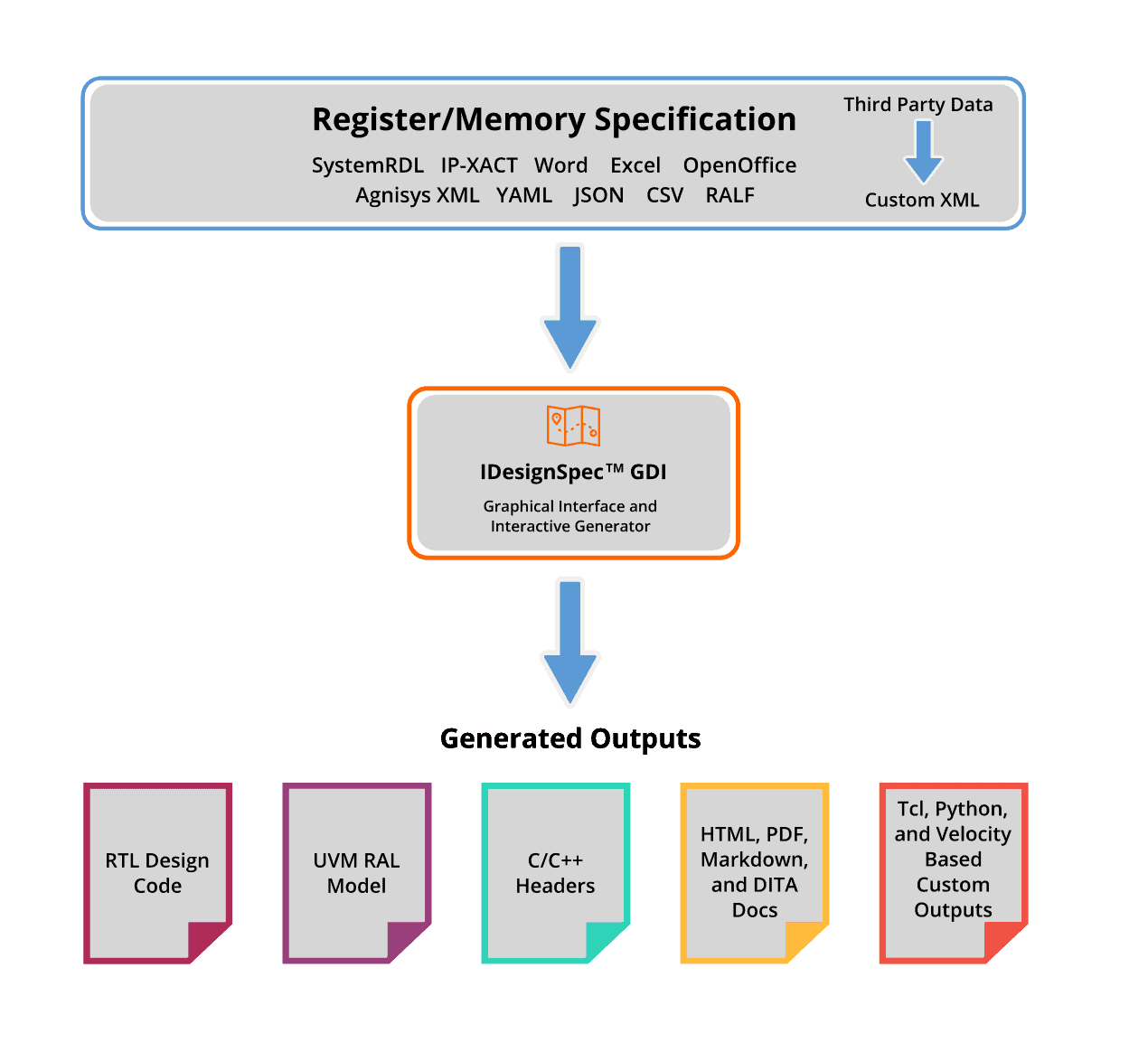

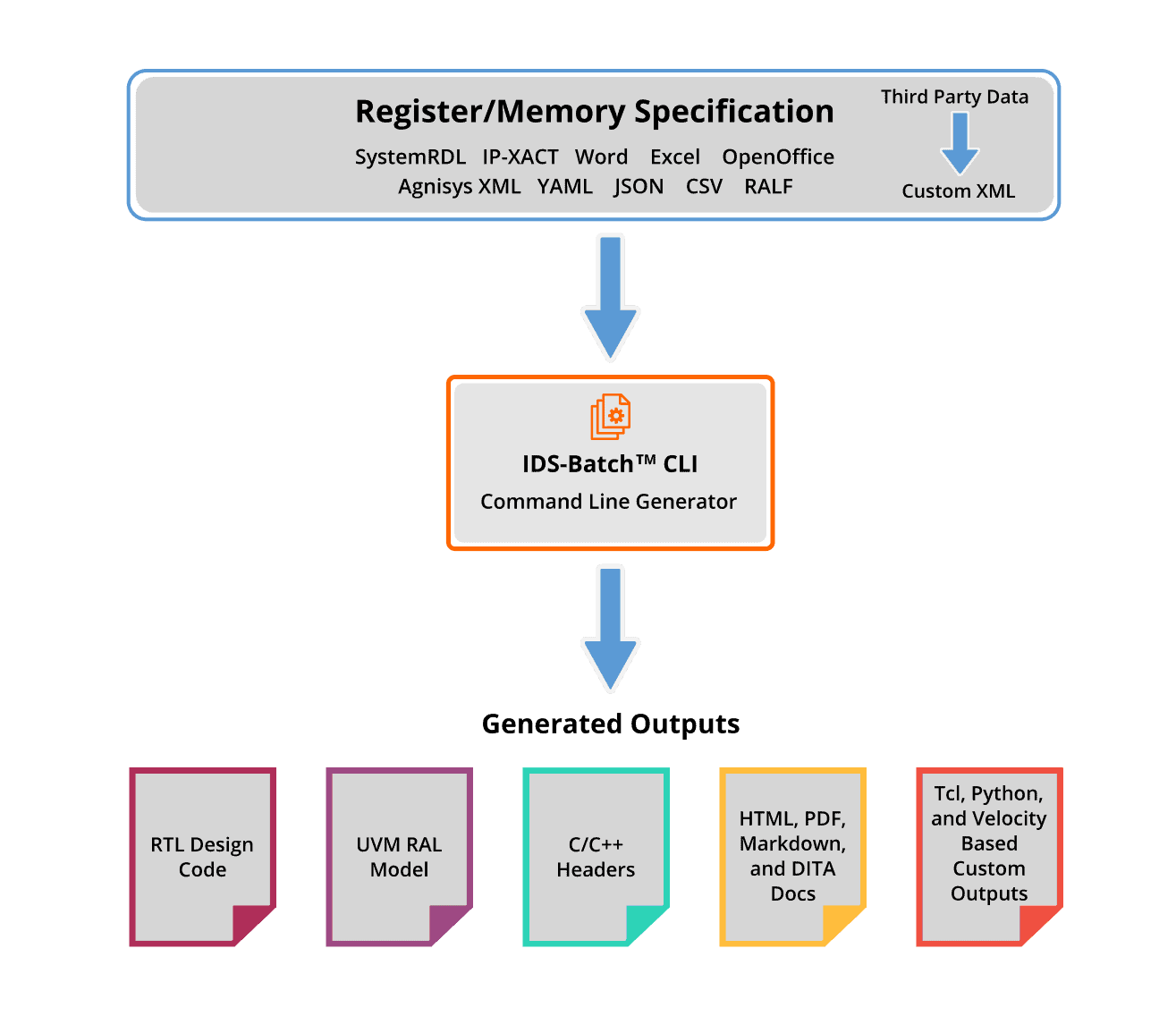

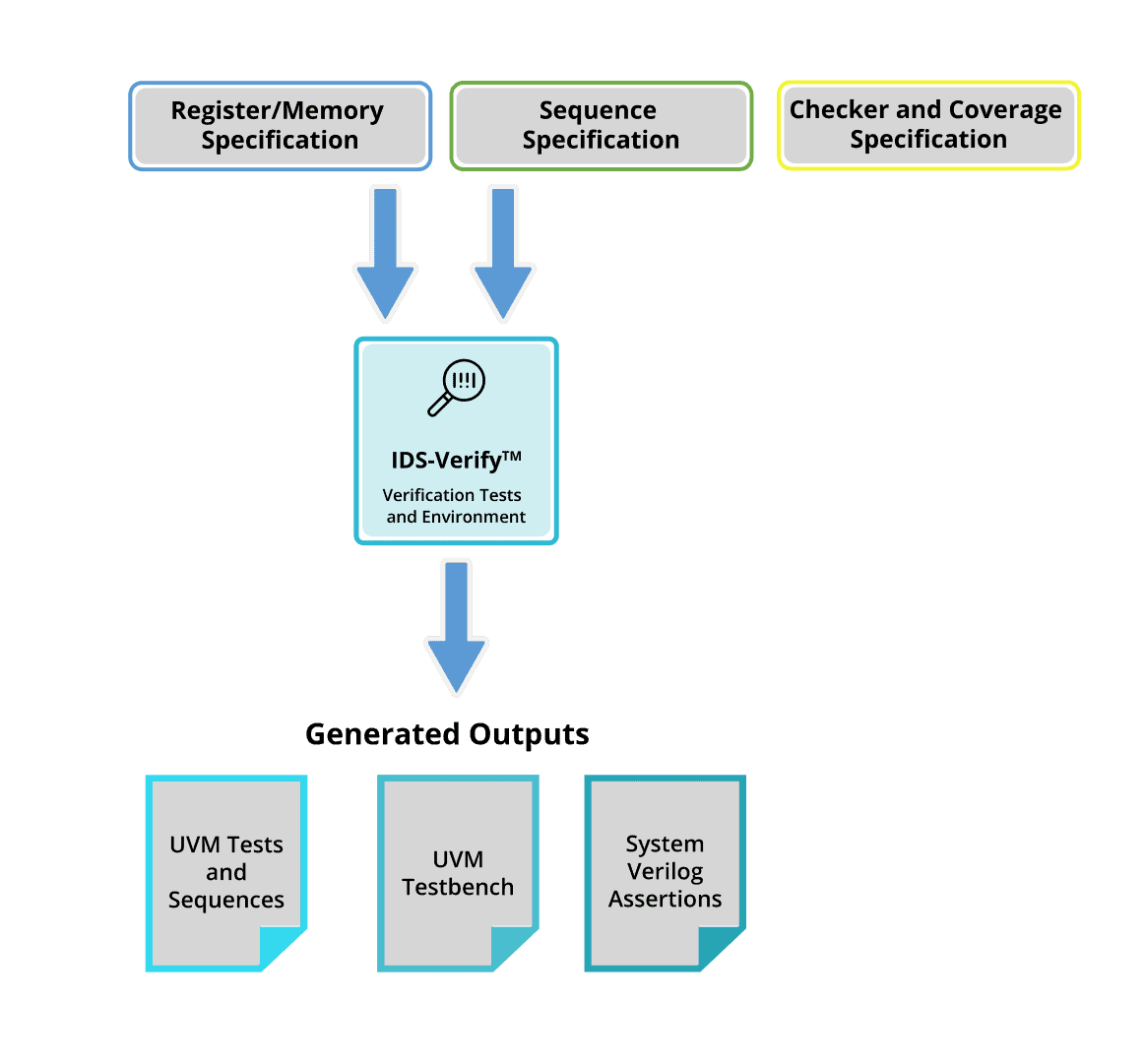

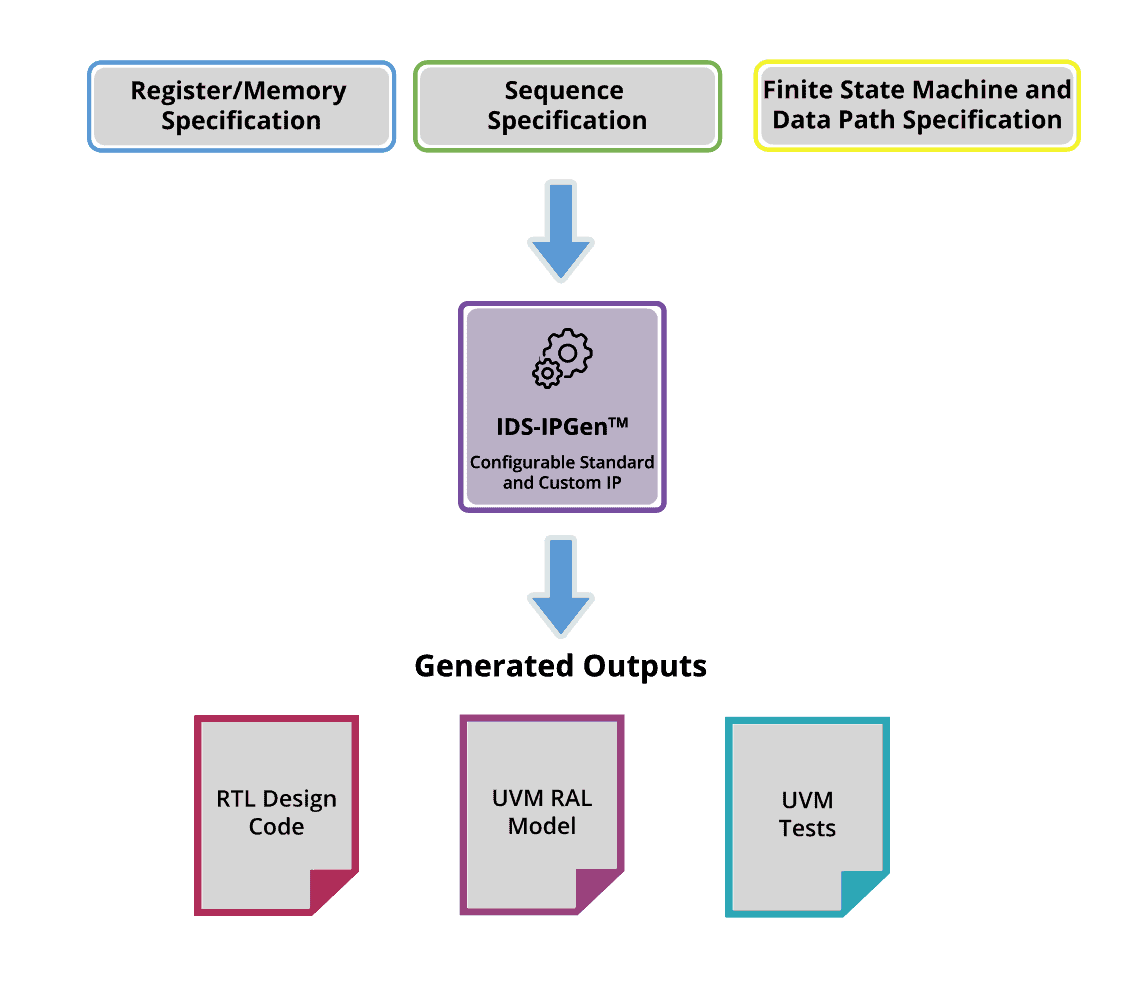

Code Generation

Based on the golden specification, various SoC teams can use the high-performance code generators via GUI or command line. The generated RTL Code (VHDL, Verilog, SystemVerilog or SystemC) for the registers is human-readable with easy-to-follow comments. The RTL also includes a bus slave and a decode logic specific to the bus protocol (AHB, APB, AXI, AXI-Lite, or proprietary), ensuring instant connection of the application logic to the register bus. The UVM Register Model Generater generates UVM verification model with Register Arrays, Memories, Indirect Access Registers, FIFO Registers and Coverage, Constraints Models and hdl_path. Users are able to customise various outputs by using our popular Velocity Template and TCL API, enabling you to meet various requirements for RTL, C++ Classes, verification code and documentation.

Special Registers

The UVM library includes examples of few commonly used special registers such as Indirect, Indexed, Alias and RO/WO Registers. But today’s SoCs demand more specialised register behaviour to meet various HW/SW interface requirements. IDesignSpec supports over 20 special registers including Shadow, Lock, Trigger-Buffer, Interrupt, Counter or External.

Document Generation

The customisable Document Generator can output file formats such as HTML, PDF, Custom PDF, .doc, .xls, DITA, IP-XACT, SystemRDL or ARM CMSIS.

David Clift, Applications Specialist, FirstEDA

David Clift, Applications Specialist, FirstEDA