ARV

ADVANCED SOC VERIFICATION TOOL / ASIC D&V

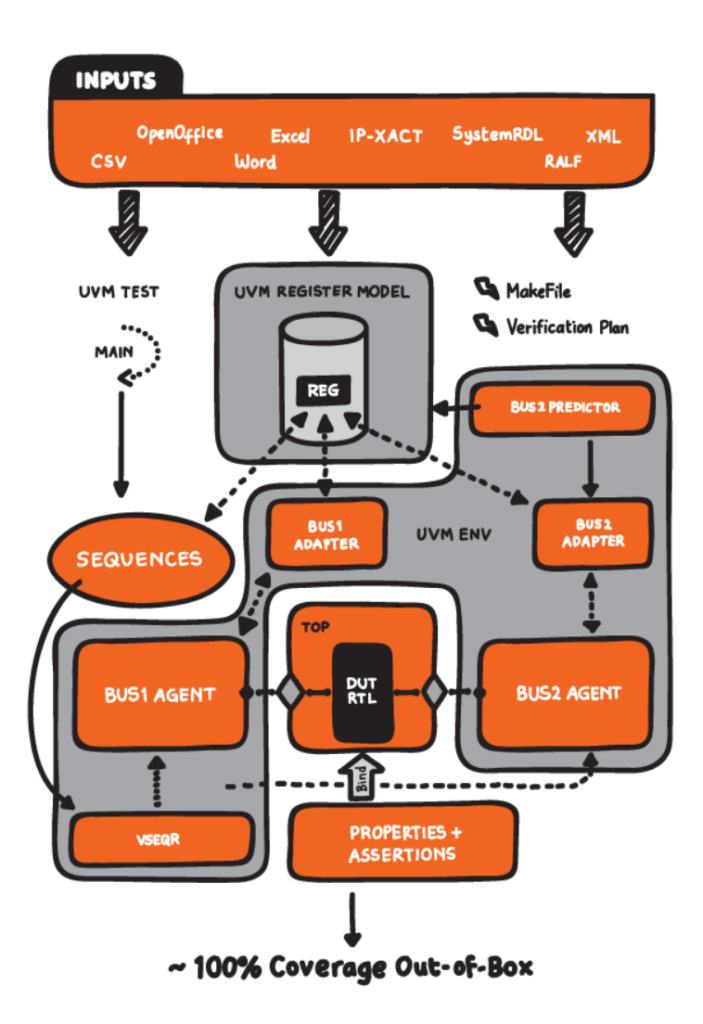

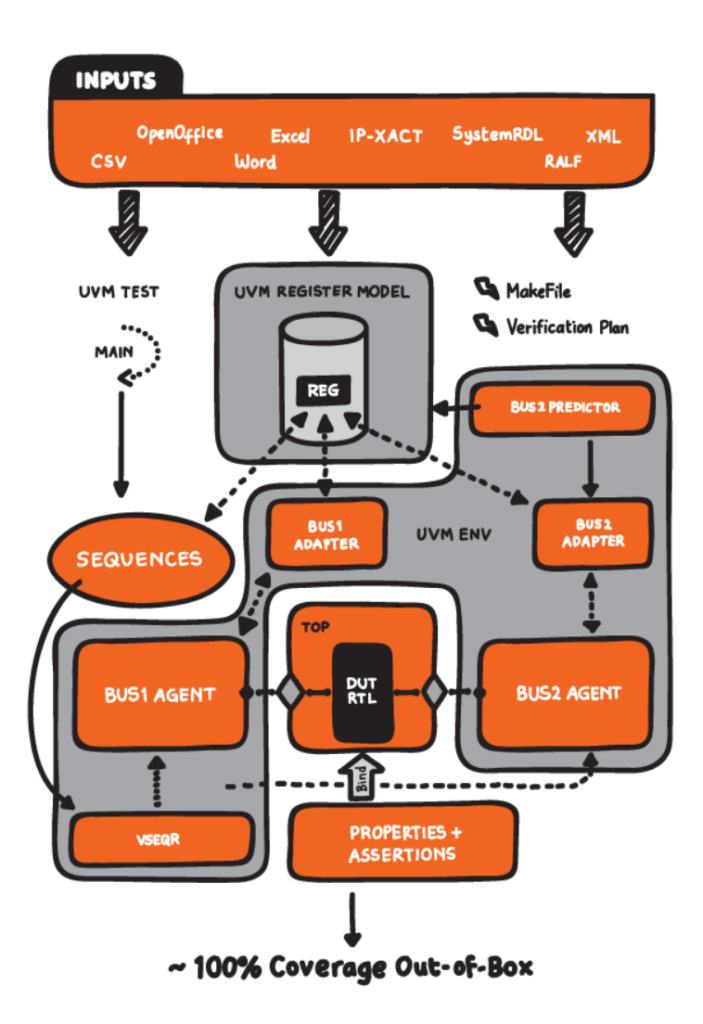

Based on the register specification, Automatic Register Verification (ARV) generates the complete UVM testbench: bus agents, monitors, drivers, adaptors, predictors, sequencers and sequences, as well as the Makefile and Verification Plan. The UVM testbench is fully connected to the UVM Register Model and DUT, providing you with a push-button verification.

Creation of the UVM test environment from scratch takes extensive time and meticulous attention. While UVM provides standard register and memory tests such as reset, bit_bash, and access, they only provide ~60% functional coverage out of the box. The user has to manually put in the effort to cover the remaining 40%. Automation that provides 100% coverage is key to verification success as IPs and SoCs grow in complexity.

UVM Sequences

Sequences are automatically generated for various types of register behaviour. These sequences are called out by a virtual sequence based on the access type of the fields. You can generate First-Level Sequences for the fields, Register-Level Sequences for registers and positive/negative sequences for Special Registers.

Verification via Simulation and Formal

Verification can be done using complementary verification methodologies. The generated files include “Makefiles” for the industry popular simulations and formal tools. In addition to direct and constrained random simulation test-cases, the entire verification process can be further improved by formally verifying IPs with the slave interface, reducing simulation runs and overheads involved in creating block-level test-benches.

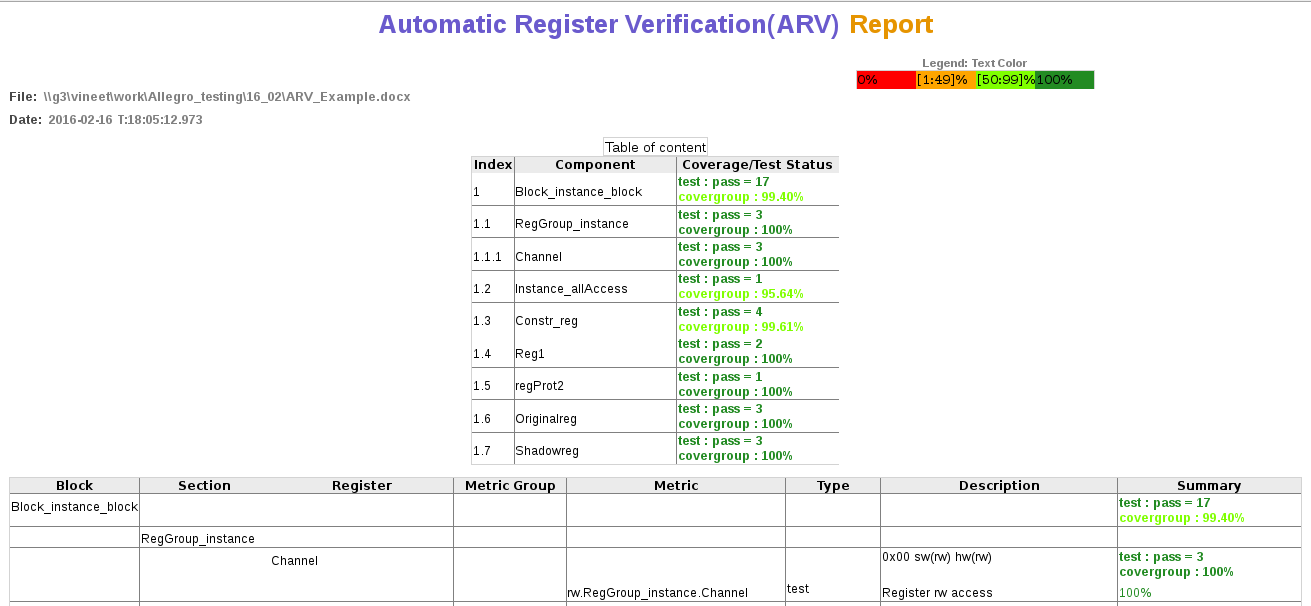

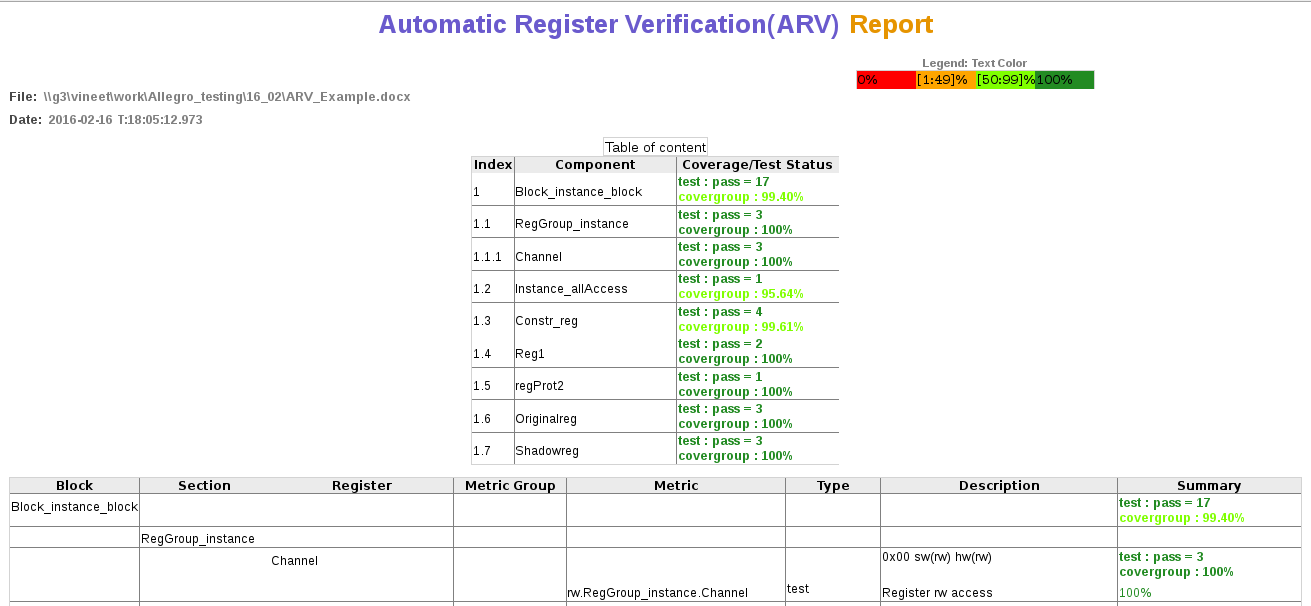

Verification Plan and Coverage Report

The generated graphical report includes a Verification Plan showing the complete summary of the coverage results and test status. The hierarchy of the IP along with functional coverage is displayed in HTML format. The data is depicted with various colours to easily get the percentage of the pass and failure of the coverage. The Zoom functionality helps you focus on a specific component and its internal hierarchy.

ARV is an add-on to IDesignSpec that auto-generates a complete UVM testbench for registers with sequences/agents for RTL simulation and assertions for formal verification, providing 100% functional coverage.

- Seamlessly integrated with commercial RTL simulation and formal tools

- Generates verification plan with back-annotation of test results

- Supports special registers including Lock, Indirect, Constraint, FIFO or Multiple-Bus Domains

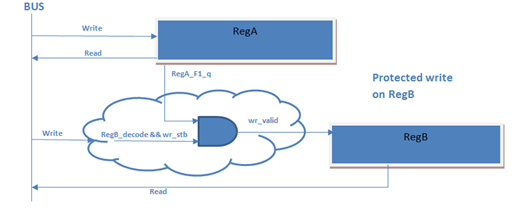

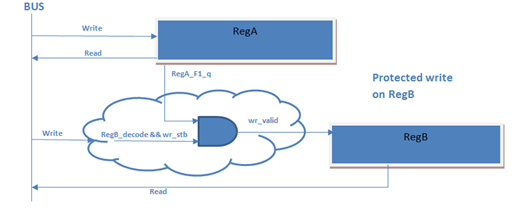

Lock register:

The software write access of a register can be locked based on the value of another register field or based on an expression consisting of different registers or fields. See the logical view of Lock Register:

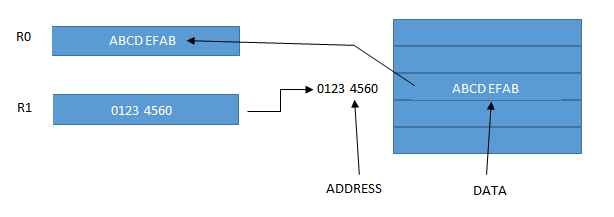

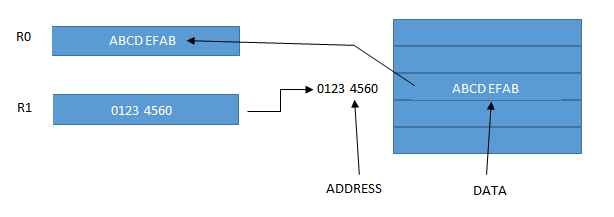

Indirect register:

Some registers are not directly accessible via a dedicated address. Indirect access of an array of such registers is accomplished by first writing an “index” register with a value that specifies the array’s offset, followed by a read or write of a “data” register to obtain or set the value for the register at that specified offset. See the logical view of Indirect register with ARV:

ARV automatically generates all of the call back classes into register model, also generates UVM sequences for special registers like Shadow Register, RO-WO pair at same address, Aliased Register, Locked Register, Trigger-Buffer Register (Wide register), Indirect Register, Interrupt Fields/Registers, Counters, FIFO Register, Paged Register, External (User Defined) Registers etc.

ARV automatically generates all of the call back classes into register model, also generates UVM sequences for special registers like Shadow Register, RO-WO pair at same address, Aliased Register, Locked Register, Trigger-Buffer Register (Wide register), Indirect Register, Interrupt Fields/Registers, Counters, FIFO Register, Paged Register, External (User Defined) Registers etc.

ARV-Formal

ARV-Formal is a complete solution that takes the register specification and RTL design as input and performs formal proof to ensure all register operations conform to the specification. ARV-Formal is powered by an embedded version of (OneSpin 360 DV Verify) to provide a one-button seamless process flow leveraging the power of modern formal verification tools. ARV-Formal automatically generates assertions directly from the specification therefore completely automating setup and ensuring a very rapid return on investment. Users are using the ARV Formal output with Mentor Questa Formal.

ARV-Sim

ARV-Sim is a complete register verification solution that integrates with Synopsys VCS, Cadence Incisive and Mentor Questa simulators. ARV-Sim automatically generates the complete package including bus agents, monitors, drivers, adaptors, predictors, sequencers and sequences required for System Verilog (SV), Universal Verification Methodology (UVM) testing. It creates the simulator make-files to completely automate the verification process. This approach eliminates the lengthy and error prone UVM test bench and sequence creation process. ARV-Sim provides the positive and negative sequences automatically – not just the test bench but also the actual test sequences that stimulates the hardware to ensure that the implementation is correct.

ARV ensures the register implementation is correct by implementing the following steps:

- ARV ensures that the coverage metrics are achieved. The only way we know we have tested all scenarios, is by the coverage. ARV provides the coverage metrics and writes tests to enable 100% coverage on the registers

- ARV supports testing of special registers, for example, lock registers, shadow registers, register aliases, interrupts etc. It generates sequences for these special registers

- Automatically creates register-focused coverage reports

- ARV doesn’t need a test bench to start testing the register implementation

- User can check either the IDesignSpec generated RTL code, the user’s own implementation, or a mix of the two with standard buses or user defined buses and transactions

- Being an add-on to IDesignSpec, it can import IP-XACT, SystemRDL, RALF, Word, Excel, CSV, XML and host of other formats

ARV-Sim, ARV-Formal Availability

- ARV-Formal and ARV-Sim are add-on products to IDesignSpec. Engineering teams may request an ARV-Formal or ARV-Sim evaluation. Also available is a detailed product datasheet and whitepaper

- ARV-Sim and ARV-Formal are immediately available on Windows and Linux (Redhat and Ubuntu)

ARV automatically generates all of the call back classes into register model, also generates UVM sequences fo

ARV automatically generates all of the call back classes into register model, also generates UVM sequences fo David Clift, Applications Specialist, FirstEDA

David Clift, Applications Specialist, FirstEDA