Nomita Goswami

FirstEDA

Nomita Goswami

FirstEDA

Here is a low power feature of IDesignSpec I would like to share with you

—

Further to my previous blog Automation in UVM Register Modelling where I introduced you to Agnisys and IDesignSpec here, I would like to share with you, its Lower Power Feature which helps in the generation of Low Power RTL models.

With the increasing number of transistors and clock frequency, a good battery life requires a low power methodology. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Often, the clock signal drives a large capacitive load, making these signals a significant source of dynamic power dissipation. Clock Gating is one of the ways to reduce power, as the reduction in switching activity during the idle period when the register is shut-off decreases the power dissipation.

Clock Gating is a common technique used to reduce power consumption in the context of application-specific integrated circuit (ASIC) design. However, in FPGAs, we usually avoid gating the clock because, in an FPGA, dedicated nets and buffers are utilized to appropriately route the clock signal to different parts of the chip. Clock Gating can interfere with the clock distribution network, for example, by forcing the clock signal to go through a general-purpose lookup table. If clock gating is utilized in FPGAs, it’s up to the designer to check that the synthesized circuits are safe.

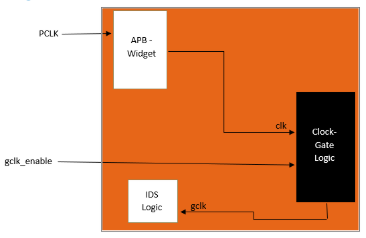

In layman terms, Clock Gating is a method to turn off the power when it is not needed. It is used by SOC design today as an effective technique to save power. In IDS, a property “clock_enable” enables the use of Clock Gating. This property can be given in any input format that the designer chooses to write their specification in, whether it is in Word, Excel or SystemRDL

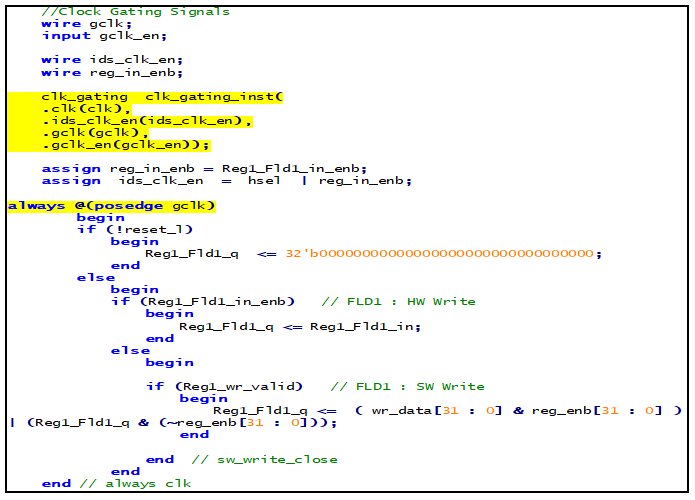

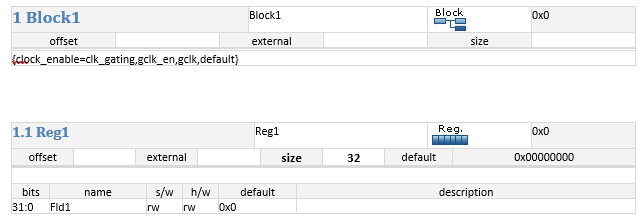

Using the ‘clock_enable’ property in IDesignSpec as shown below; the user can define their own logic for gated clock which is instantiated in the IDS block:

clock_enable=<name of the gated clock logic>, <gated clockenb>, <name of the gated clock>

‘clock_enable’ can also take a fourth argument ‘default’ as shown below by which the clock gating logic will be automatically generated and instantiated in IDS block.

clock_enable=<name of the gated clock logic>, <gated clockenb>, <name of the gated clock>,<default>

This property has been applied on the Block1 in IDSWord as shown below.

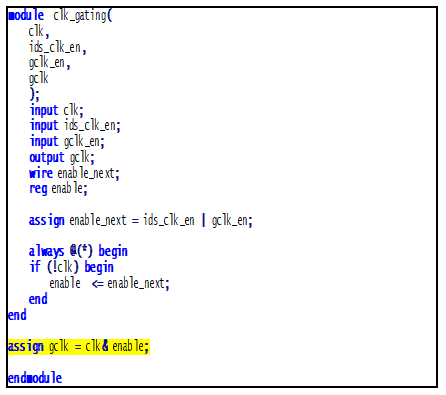

Using the specification above; the clk_gating module gets generated and gets instantiated in the RTL model, as shown below.