Zibi Zalewski

ALDEC General Manager, Hardware Division

Zibi Zalewski

ALDEC General Manager, Hardware Division

Where does the time go…

—

At this year’s Design Automation Conference, held on June 3, 4 and 5 in Las Vegas and about 11 miles away from our head office in Henderson, we celebrated our 35th anniversary with a resounding reaffirmation of our raison d’etre: the provision of verification solutions for industry’s pressing challenges.

We had on display a variety of solutions – both hardware and tools-based – and it was most pleasing to see the high level of interest shown by engineers. Most had an immediate or imminent need for something on display, confirmation that not only were our selections of which products to showcase good ones but that Aldec continues to serve genuine needs within the engineering community.

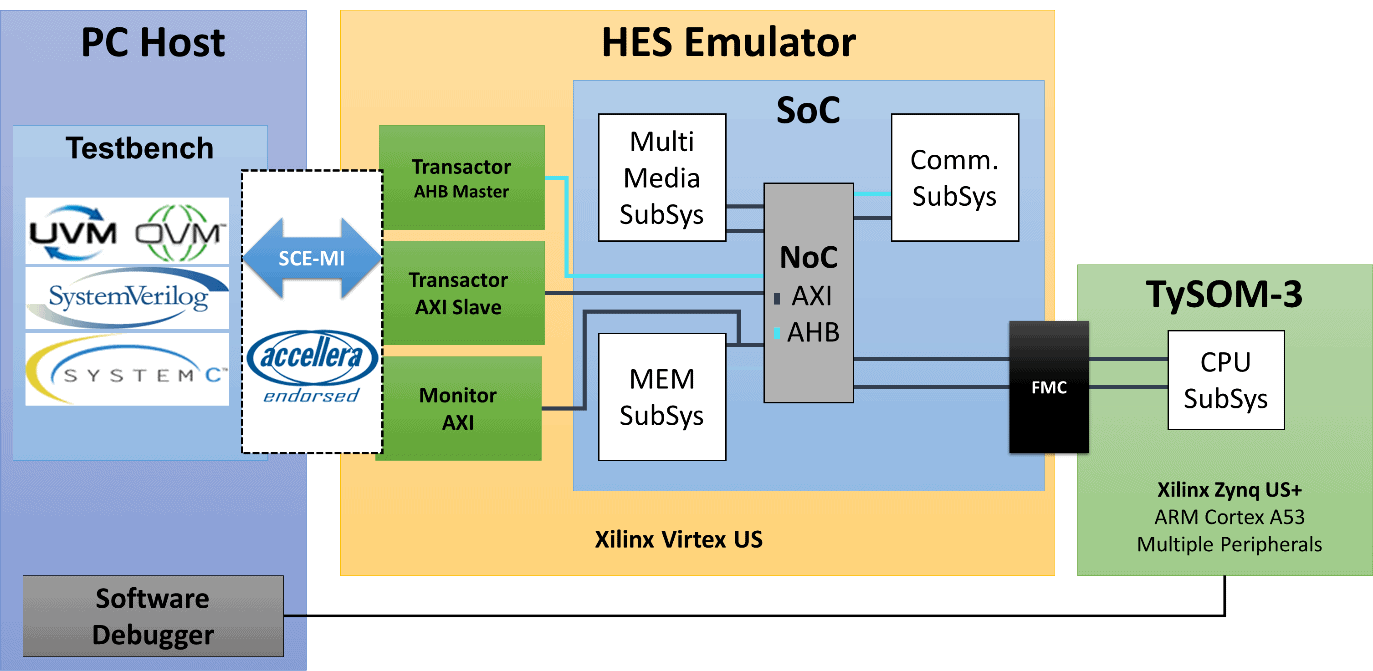

As General Manager of Aldec’s Hardware Division, I was particularly pleased by the interest shown in a hybrid co-emulation demo we gave, and which solves a major problem hardware and software engineers face when collaborating on the verification of their respective design parts. Specifically, hardware is typically verified out of context with the software, and vice versa. For example, the software engineers verify on models of hardware (which can be very expensive, and which run slowly).

On the premise that the SoC or ASIC under development is likely to contain an ARM core, we simply said: OK, let’s ‘share’ the one in the Xilinx Zynq US+ FPGA on one of our high-end TySOM-3 boards (a platform which itself support the co-development of hardware and software) with our HES-US-440 hardware emulation platform.

The ‘sharing’ was facilitated by an FMC Host2Host bridge and negates the need for the hardware team to purchase RTL code for the ARM cores. Also, prototype-level clock speeds are achieved which is of immense benefit to the software team. For example, Linux (running on a hard Mali-400 GPU core) will boot within minutes as opposed to hours, which would be the case under a modelling scenario.

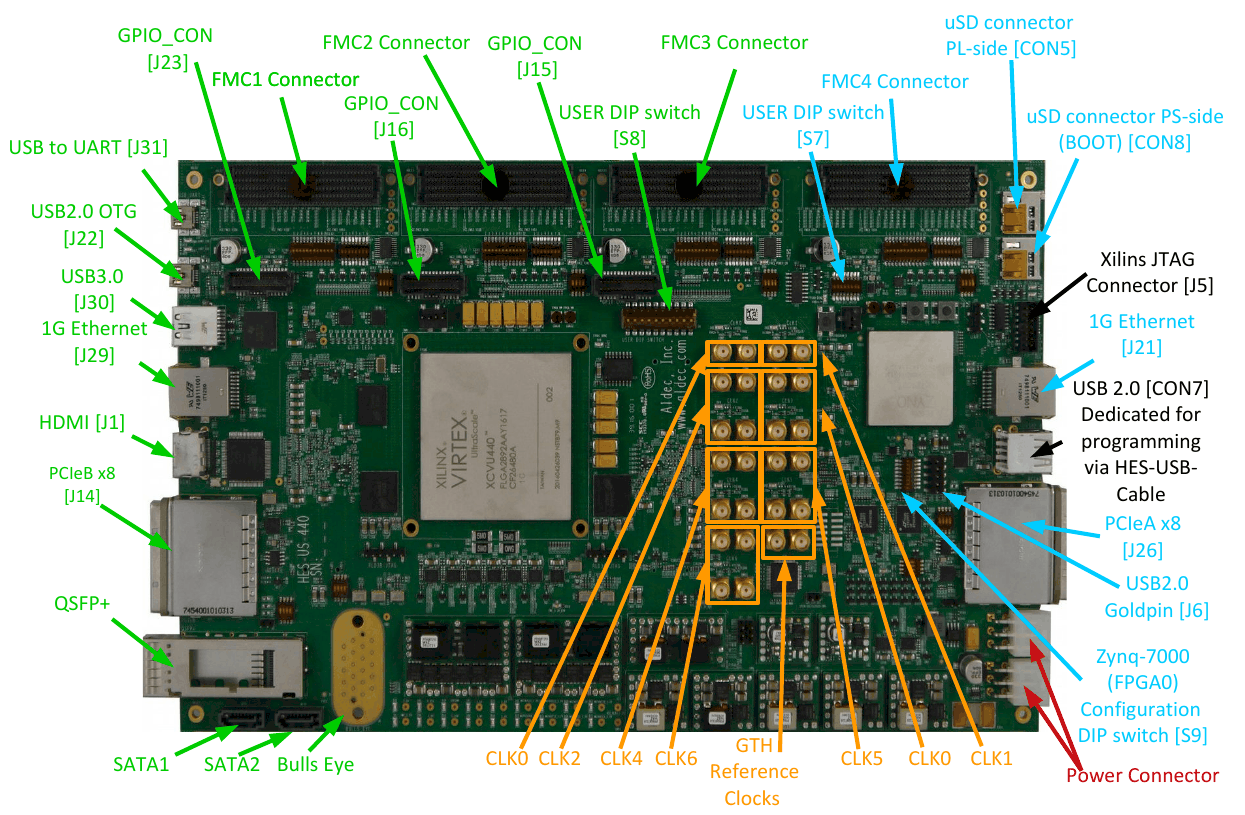

In addition, the HES board provides a wealth of interfaces and I/O (with corresponding drivers) for accessing resources that will be embedded alongside the SoC/ASIC under development, as well as interfacing with the outside world.

However, this was just one of the demos that wowed the visitors to our booth at DAC. Other demos we can discuss in subsequent blog. For me though this was that one that exemplified what Aldec’s all about; helping engineers be productive through the presentation of a solution that is practical delivers multiple benefits.