Nomita Goswami

FirstEDA

Nomita Goswami

FirstEDA

Having worked as a Hardware Design and Verification Engineer myself for many years, joining FirstEDA as an Applications Specialist was quite a big change

—

As part of my new role, I was assigned product responsibility for supporting the Agnisys tools and solutions. Centred around their IDesignSpec (IDS) tool, Agnisys have developed a suite of solutions for automating register management, register specification and register verification. Despite my many years of experience on the engineering side of the fence, this was a new topic for me and I would be lying if I told you I wasn’t a little bit intimidated!

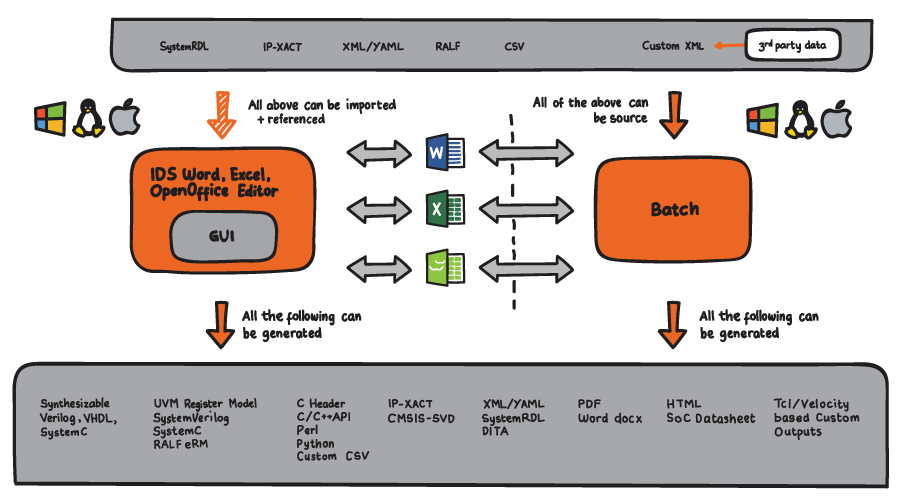

For those of you who are not familiar with Agnisys IDS, it aids in creating a centralised Executable Register Specification, that allows users to automatically generate Synthesisable Models, C headers, UVM Models, UVM testbenches and much more; tasks that are usually undertaken manually, which is very time consuming, tedious and error-prone.

Having no prior experience of the tools, and not being from a software background, I spent the next couple of days watching various videos and recorded webinars, to understand the workflow and how to implement it effectively. I was also getting more familiar with the many special registers that are supported by Agnisys and which are often required in today’s IPs (such as Lock Registers, Shadow Registers, Interrupt Registers, Counters, etc.).

I was happy to find that there are various GUI options for IDS, even capable of handling input from Microsoft Word and Excel, which greatly simplifies use for those who are not familiar with specific input standards such as SystemRDL. With this knowledge I planned to first explore the tool using Word and Excel, with a view of graduating to SystemRDL at a later stage.

I found that IDS was very easy to install and that once it was up and running it didn’t take long at all to generate RTL and UVM verification outputs. I had never seen automatically generated RTL and UVM testbenches before, let alone at the click of a button! I was pleasantly surprised to say the least. Having used UVM before, I am aware that it takes quite a bit of effort to create a fully working testbench, and can therefore fully appreciate how much time and effort this tool could actually save.

Fired up on the possibilities, I dived further into the documentation. It didn’t take long to establish that in IDS I have all the control and flexibility needed to change or modify the generated RTL and UVM Models! There are hundreds of supported user-defined properties, which is very impressive and I quickly began to appreciate how IDS could become an integral part of the tool flow, especially for those companies creating lots of IPs. This became even more evident when I started working with customers and receiving their ‘real world’ insights and feedback during evaluation and use.

I will be writing further blog posts regarding the Agnisys tools as I continue to learn more about the capabilities and methodology myself. I hope to convey how easy it is to pick it up and quickly start getting value from IDS in particular. So please stay tuned! In the meantime, if you would like to learn how your team can benefit from IDS and the wider Agnisys ecosystem, I will be delighted to provide a demonstration. Please do not hesitate to contact the FirstEDA team with any questions at all.