ISequenceSpec

AUTOMATICALLY GENERATE UVM SEQUENCES / ASIC D&V

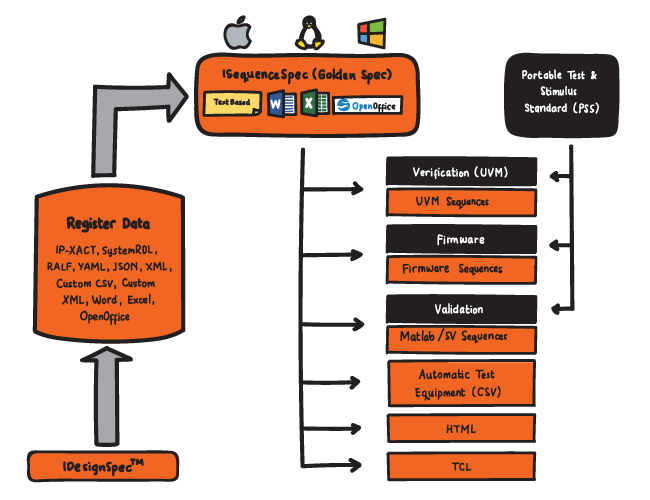

ISequenceSpec enables users to describe the configuration, programming and test sequences of a device and automatically generate sequences that are ready to use during early verification stages, firmware development and post-silicon validation.

From a single sequence specification, you can generate UVM sequences for verification, C code for firmware and device driver development, SystemVerilog sequences for validation, and various outputs including CSV for Automatic Test Equipment.

A common Sequence specification serves as a powerful tool for stimulus generation used by multiple teams involved in verification, firmware and post-silicon validation stages. But most SoC teams lack a unified flow for creating sequences – each team has to manually write sequences in their formats, thus wasting time and resources.

ISequenceSpec auto-generates test and configuration sequences for custom IPs. Users can define the sequences in pseudo-code and retarget the sequences in various languages including UVM sequence for simulation, C for firmware tests and C/ASCII/CSV for post-silicon validation.

- Sequence editor available in Word, Excel or Python text

- Capture hierarchical sequences at a higher level in-sync with register specification

- Sequence constructs include fork/join, constraints and randomisation, loops, if-else, wait, arguments, constants, in-line functions

Our customers challenged us to “do for sequences what we did for registers”. In creating ISequenceSpec, we used the lessons learnt from years of enhancing IDesignSpec.

Ian Gibbins, Applications Specialist, FirstEDA

Ian Gibbins, Applications Specialist, FirstEDA