David Clift

FirstEDA

David Clift

FirstEDA

As an engineer and habitual tinkerer, mender and builder, I have built up a vast array of various tools for different jobs

—

Amongst these tools, as is often the case with any toolbox, there are a collection of “Special” tools. The tools you just love to use. Maybe because they just do exactly what they were designed for perfectly, or maybe because they just feel good in the hand. It could even be that these tools hold special memories… I have an old Sandvik 26” hand saw for example, that had originally belonged to my grandfather. I do have other crosscut saws, but this saw is special. The handle shape seems just right, it has an effortless cut and it’s always a pleasure to use. Now shouldn’t the tools we use day to day in our ASIC/FPGA development work be the same?

When you are developing HDL, you spend many hours working with your HDL editor. Just like my old saw, the interface of your editor should feel comfortable to use. It should also have features that make it a pleasure to use and that make your day to day tasks easier. I have used a number of different editors over the many years I have been coding, but my current ‘go to’ tool is Sigasi Studio XPRT. I find it has all the refinements I need to make hardware design easier, more efficient and dare I even say fun.

At its core is a built-in compiler, meaning that the tool understands your code while you type, providing instant feedback on errors and autocomplete suggestions. But Sigasi Studio also has many other valuable features to ease the process of HDL design, to help the user to produce higher quality code and reduce the amount of time required for code review. So, here’s a quick list of some of my top Sigasi Studio features:

I guess this shows my preference for VHDL over Verilog, as stuttering is a VHDL only feature. In VHDL there are a number of different two-character operators; we have schedule <=, assignment := and choice =>. These little two-character operators pop-up all over your code, some of which will be picked up by the template system and filled in automatically (more on this later) but most won’t. So what is stuttering? Stuttering is an editing technique popularised by Emacs, that allows you to type certain things really fast. Stuttering means that you tap a certain key twice and it expands into something more complex. For example, press the period key ‘.’ twice, and the editor will expand it to a right arrow =>. Stuttering works like double clicking.

The following stuttering keys are available in Sigasi Studio:

Keys Effect

,, <=

.. =>

:: :=

Has this ever happened to you? Having reused a section of code from a previous design, you then decide that for the new design a signal name change would make things clearer for the new intended function. But this signal isn’t used in just a few places, it’s a port and the entity is used in a number of different locations throughout the design. Simple search and replace will not fix this, but Sigasi Studio can, as it’s syntactically and semantically aware of your design. This means it can perform context aware renaming; renaming the signal in the original entity and architecture, as well as all the files in the design that use it.

By letting Sigasi Studio take all the load, this simple feature can save hours! I have actually produced a short demonstration video on refactoring in Sigasi Studio, which can be viewed on the FirstEDA YouTube channel .

Whenever I was using a new editor, one of the first tasks was always to get it working with the compiler, so that I could write a section of code and then at a key press have the editor save and submit it to the compiler for syntax checking. This kind of worked, unless your code was incomplete, and as long as it was easy to feed the compiler results back to the editor in some way… Well, because of Sigasi Studio’s built in compiler, this is now a thing of the past!

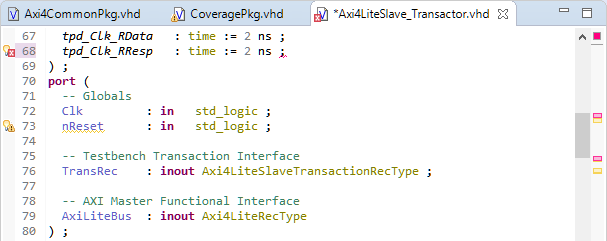

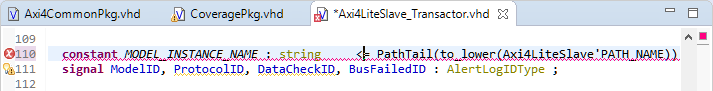

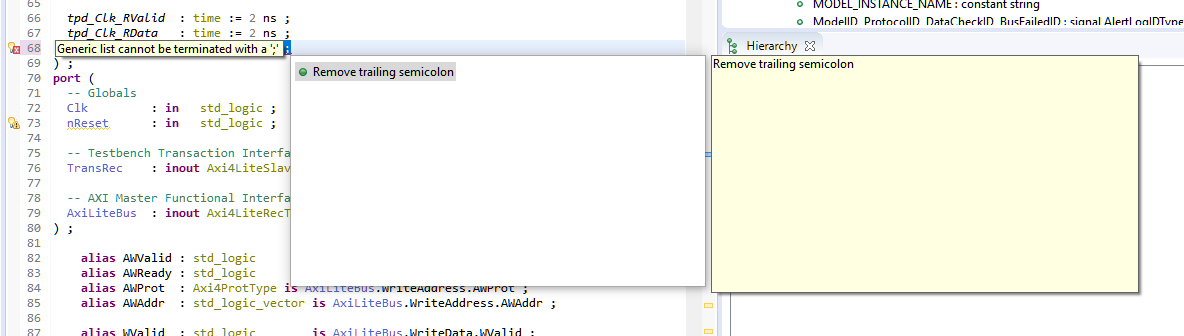

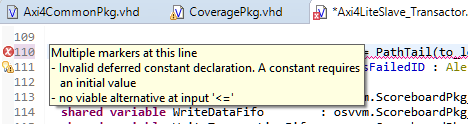

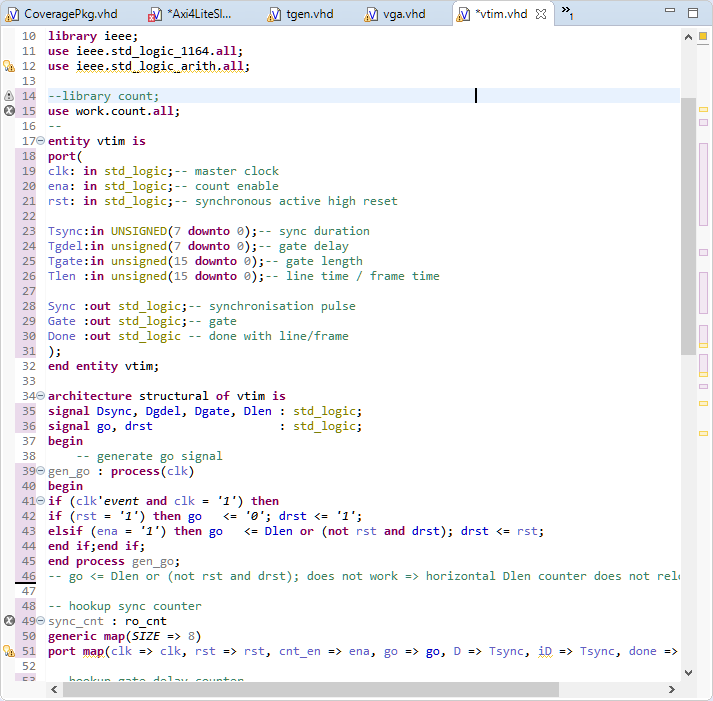

The tool is constantly checking my code as I type and because it is language aware, it knows that I don’t need that ‘;’ after the last port on my entity and will warn me if I leave it there. Also, if I do save a file with errors in it, Sigasi Studio will display all of those errors in the error panel and allow me to jump straight back to them. Remember this works even if your code isn’t complete and as a further aid, for a large number of errors Sigasi Studio will provide a quick-fix to resolve the issue.

Figure 1- Line 68 – Syntax Error Line 73 – DRC Warning

Figure 2- Syntax error Line 110 no quick fix

Figure 3 – Quickfix for syntax error at Line 68

Figure 4 – Description of two errors at line 109

How you format your code has absolutely no effect on how it simulates or synthesises. If you want to see poorly formatted HDL code, get a computer to auto generate some for you! But good consistent formatting makes code easy to read and understand. If you can understand code, then maintaining it becomes easier. I have seen some poorly formatted code in my time and it always makes me think that if you cared so little about something as easy as making your code readable, how much did you care about the quality of your design?

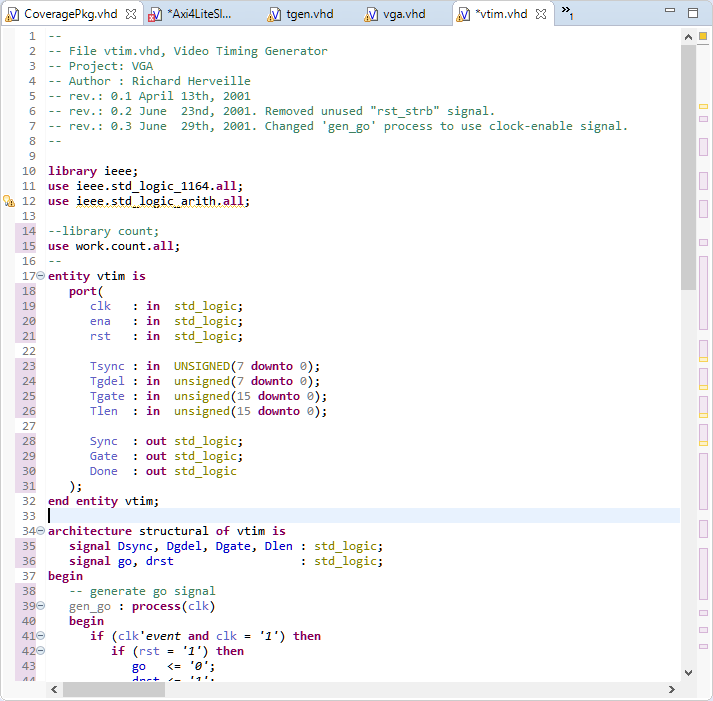

Sigasi uses smart formatting, so your code should always come out well formatted as you type. But because we don’t always type all of our code (we cut-n-paste from old designs, from design ideas we tried but didn’t use before… I even know people who have used code they found on the internet) there is the formatter. Just press Ctrl+Shift+F and your code will be smartly formatted with a repeatable style, meaning all your coding looks consistent.

Figure 5 – An example of badly formatted code

Figure 6 – The same code after formatting

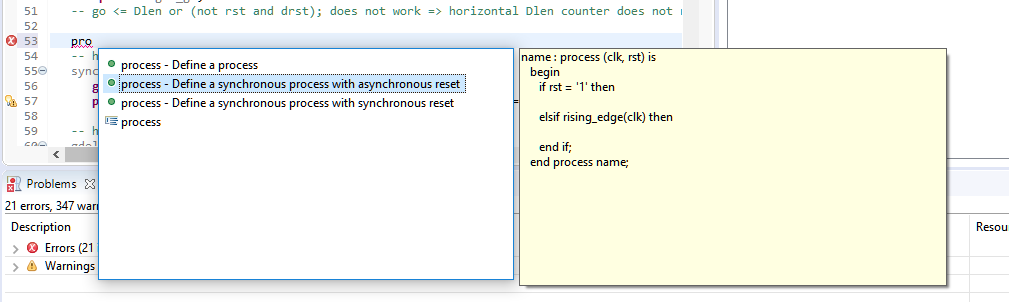

Despite my experience with HDL’s (I teach VHDL) I do still occasionally find Verilog constructs creeping into my VHDL and visa versa… So having a tool that is not just aware of the syntax, but one that is both syntactically and semantically aware is just great! Sigasi Studio will give me keyword completion when I ask; just click Ctrl + Space and there’s a helpful dialogue, with not just language keywords but data objects, entity declaration or instantiations – whichever is appropriate for the area of code I am in.

Figure 7 – Code completion

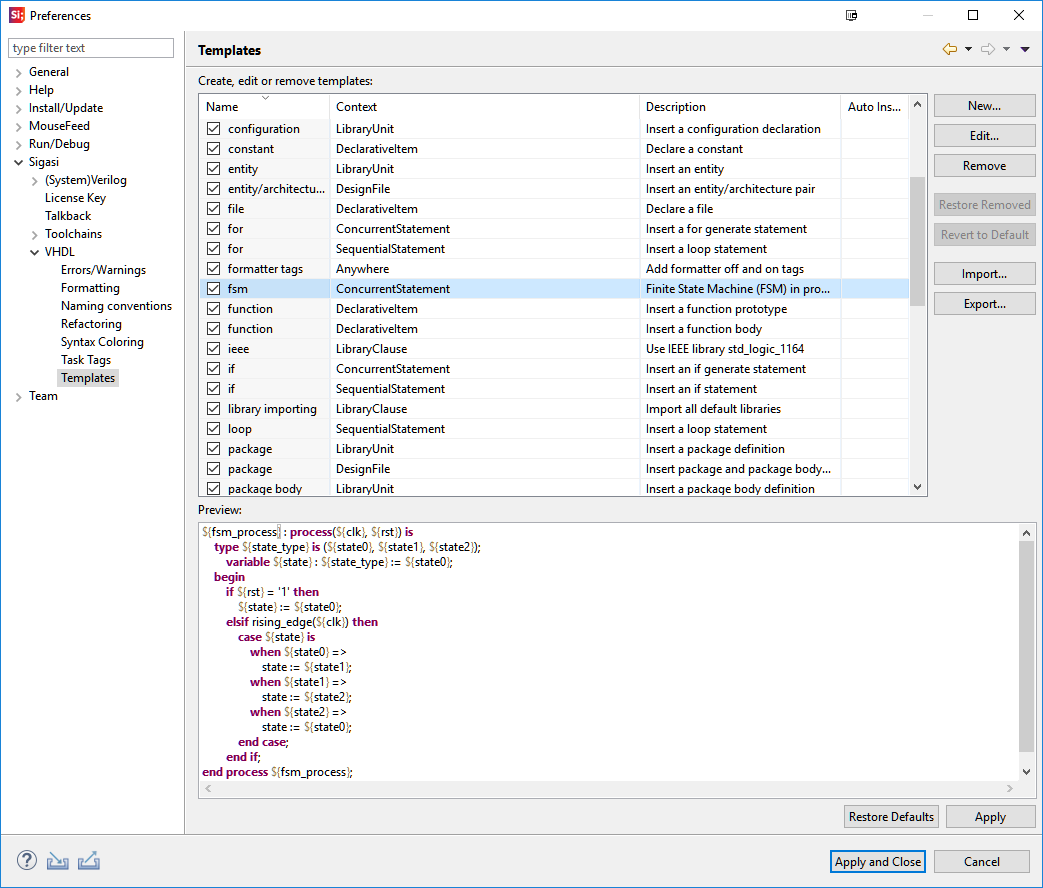

Working alongside the keyword completion is the template system. Templates result in small fragments of reusable code that have certain pieces left open for you to fill in. This might sound a bit complicated, but templates are actually very simple to use. They are also very powerful. Not only does the default installation of Sigasi come with over 50 templates for VHDL and 25 for SystemVerilog, but the system is expandable and can be customised to your own coding needs.

Figure 8 – Template setup for VHDL

So, those are some of my favourite features in Sigasi Studio. I say ‘some’, because there are plenty more features that make the tool such a pleasure to work with. I could have easily added to that list the VHDL Library setup or the SystemVerilog class hierarchy viewer, or even the integration with Aldec’s DRC tool ALINT-PRO… But I’ll save those for another day (I have already recorded a video on the ALINT-PRO integration – again on the FirstEDA YouTube channel). Stay tuned for another post soon.

If you have any questions at all regarding Sigasi Studio or would like to arrange a full demonstration or evaluation, then please feel free to contact myself or the team at FirstEDA and we’ll be very happy to help.