Breker

PORTABLE STIMULUS

FPGA / SAFETY / ASIC / FV / HW-V

PORTABLE STIMULUS

FPGA / SAFETY / ASIC / FV / HW-V

Given the continual increase in IC design size and complexity, as well as specific advances—such as Artificial Intelligence (AI), open processor instruction sets, and safety / security requirements—traditional verification methods no longer scale to modern needs. As such, the verification market is constantly evolving. Test content and testbench production has experienced the most radical evolution of all of the verification technologies over the last 20 years, and it is still this aspect of the process that causes development teams the greatest challenges. It is this area on which Breker has focused its attention, producing highly effective test suite synthesis solutions that have gained widespread adoption.

Breker Verification Systems is a leading provider of verification synthesis solutions that leverage SystemUVM, C++ and Portable Stimulus, a standard means to specify reusable verification intent. It is the first company to introduce graph-based verification and the synthesis of high-coverage test sets based on AI planning algorithms. Breker’s Test Suite Synthesis and TrekApp library allows the automated generation of high-coverage, powerful test cases for deployment into a variety of UVM, SoC and Post-Silicon verification environments. Case studies that feature Altera (now Intel), Analog Devices, Broadcom, IBM, Huawei and other companies leveraging Breker’s solutions are available on the Breker website. Breker is privately held and works with leading semiconductor companies worldwide.

The Breker tool suite and TrekApps have been proven in production at many leading semiconductor companies worldwide, earning a reputation for dramatic verification schedule reduction in advanced development environments. Breker’s solutions enable design managers and verification engineers to realize measurable productivity gains through GRAPH-based scenario description, speed coverage closure by PORTING the same tests across verification platforms, and easily SHARE verification knowledge.

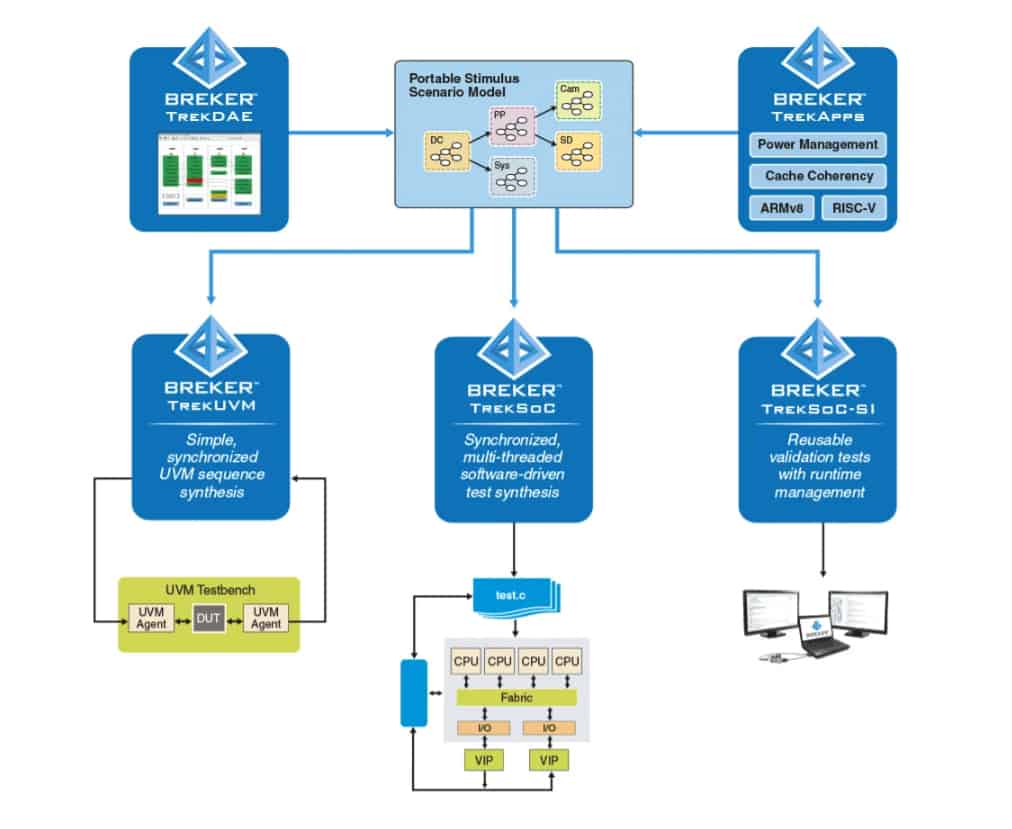

TrekUVM uses the same scenario model format to generate Universal Verification Methodology (UVM) test cases for transactional testbenches, all but eliminating the notorious complexity of UVM sequence authoring.

TrekSoC helps customers develop intuitive models based on the PSS to describe the verification space, and then use these models to automatically generate SoC test cases including stimulus, expected results and coverage detail.

TrekSoC-Si enables all of the testbench capability contained in TrekUVM and TrekSoC to be applied to hardware verification solutions including Emulation, Prototyping Systems and to the final device, post-fabrication.

The Design Analysis Environment user interface provides unique visual graph construction, graph visualization, and multi-threaded runtime test inspection capabilities. It operates across all of the Breker tool suite and TrekApps, enabling a consistent use and feel for the tools. The new visual graph editor allows for fast scenario construction and comprehension.

The entire tool suite makes use of graph-based scenario models created using either the new Accellera Portable Stimulus Standard DSL or C++ formats, or coded in native C++. The models may also be entered using the Breker visual editor, or generated from one of the TrekApps. These modeling options provide easy methods to build powerful and complete models of verification intent.